SC03/B1

RM03/RM05/RM80 COMPATIBLE

DISK CONTROLLER

TECHNICAL MANUAL

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

SC0351001-00 Rev E November, 1987

Copyright (C) 1982 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

# TABLE OF CONTENTS

| Section 1                                                                                                                                                                                                                                                                         | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 $1.1.1$ $1.2$ $1.2.1$ $1.3$ $1.3.1$ $1.3.2$ $1.3.3$ $1.3.4$ $1.3.5$ $1.3.6$ $1.3.7$ $1.3.8$ $1.4$ $1.4.1$ $1.4.2$ $1.4.3$ $1.4.4$                                                                                                                                             | SCOPE<br>Register Addresses in this Manual<br>OVERVIEW<br>General Description<br>FEATURES<br>Microprocessor Design<br>Packaging<br>Self-Test<br>Buffering<br>Error Correction<br>Dual Port Mode<br>Dual Access Mode<br>Option and Configuration Switches<br>FUNCTIONAL COMPATIBILITY<br>Media Compatibility<br>Disk Mapping<br>Diagnostics<br>Operating Systems | $ \begin{array}{c} 1-1\\ 1-1\\ 1-1\\ 1-1\\ 1-1\\ 1-1\\ 1-2\\ 1-2\\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Section 2                                                                                                                                                                                                                                                                         | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\begin{array}{c} 2.1\\ 2.2\\ 2.2.1\\ 2.2.1.1\\ 2.2.1.2\\ 2.2.1.3\\ 2.2.2\\ 2.2.3\\ 2.2.4\\ 2.2.5\\ 2.3\\ 2.3.1\\ 2.3.1.1\\ 2.3.1.1\\ 2.3.1.2\\ 2.3.2\\ 2.3.2\\ 1.2\\ 2.3.2.1\\ 2.3.2.2\\ 2.3.2.1\\ 2.3.2.2\\ 2.3.2.3\\ 2.4\\ 2.4.1\\ 2.4.2\\ 2.4.3\\ 2.4.4\\ 2.4.4.1\end{array}$ | B Cable Connector<br>Test Connectors<br>Switches<br>LED Indicator<br>Firmware PROMs<br>Bootstrap PROMs<br>INTERFACES<br>Disk Interface                                                                                                                                                                                                                          | 2-1<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-5<br>2-5<br>2-5<br>2-5<br>2-5<br>2-7<br>2-7<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9<br>2-11 |

| 2.6.5                                                                                                                                                                                                         | Header Field Handling<br>GENERAL PROGRAMMING INFORMATION<br>Clearing the Controller<br>Interrupt Conditions<br>Termination of Data Transfers<br>Ready Bits<br>22-Bit Memory Addressing<br>Line Time Clock (LTC)<br>Bootstrap Routines<br>DUAL CONTROLLER OPERATION<br>Dual Port Drives<br>Unseized State<br>Seized State<br>Returning to the Unseized State<br>DEC Compatibility<br>Dual Port Drives in a Single Port                                                                                                                                | $\begin{array}{c} 2-11\\ 2-11\\ 2-12\\ 2-12\\ 2-12\\ 2-13\\ 2-13\\ 2-14\\ 2-14\\ 2-14\\ 2-15\\ 2-15\\ 2-15\\ 2-15\\ 2-15\\ 2-16\\ 2-16\end{array}$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                               | Mode<br>Dual Access Mode<br>Dual Port Drives Busy Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-17<br>2-17                                                                                                                                       |

| 3                                                                                                                                                                                                             | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                    |

| 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.3<br>3.4.1<br>3.4.2<br>3.4.1<br>3.4.2<br>3.4.4<br>3.4.4.1<br>3.4.4.2<br>3.4.4.4<br>3.4.4.4<br>3.5<br>3.5.1<br>3.5.2<br>3.6.1<br>3.6.2<br>3.6.3<br>3.7<br>3.7.1 | Drive Placement<br>Local/Remote<br>Sectoring<br>Index and Sector Pulse Selection<br>Unit Addressing<br>Lark Drive Configuration<br>SYSTEM PREPARATION<br>Powering Down the System<br>CONTROLLER SETUP<br>Controller Address Selection<br>Interrupt Vector Address<br>Drive Configuration Selection<br>Options<br>Q-Bus Terminator Option<br>Bootstrap PROM Option<br>22-Bit Memory Addressing<br>Line Time Clock Option<br>PHYSICAL INSTALLATION<br>Slot Selection<br>Mounting<br>CABLING<br>A Cable<br>B Cable<br>Grounding<br>TESTING<br>Self-Test | 3-2<br>3-2<br>3-2<br>3-2<br>3-4<br>3-4<br>3-4<br>3-4<br>3-4<br>3-5<br>3-6<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8    |

| 3.7.2                                                                                                                                                                                                         | Register Examination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-9                                                                                                                                                |

\_\_\_\_\_

Section

| 3.7.3<br>3.7.4                                                                                                                                                                      | Hardware Formatting the Disk<br>Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-9<br>3-9                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 4                                                                                                                                                                           | CONTROLLER REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                               |

| $\begin{array}{c} 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \\ 4.18 \\ 4.19 \\ 4.20 \\ 4.21 \end{array}$ | DISK ADDRESS REGISTER (RMDA)<br>CONTROL/STATUS REGISTER 2 (RMCS2)<br>DRIVE STATUS REGISTER (RMDS)<br>ERROR REGISTER 1 (RMER1)<br>ATTENTION SUMMARY REGISTER (RMAS)<br>LOOK-AHEAD REGISTER (RMLA)<br>DATA BUFFER (RMDB)<br>MAINTENANCE REGISTER 1 (RMMR1)<br>DRIVE TYPE REGISTER 1 (RMMR1)<br>DRIVE TYPE REGISTER (RMDT)<br>SERIAL NUMBER REGISTER (RMDT)<br>SERIAL NUMBER REGISTER (RMDC)<br>DESIRED CYLINDER REGISTER (RMDC)<br>HOLDING REGISTER (RMHR)<br>MAINTENANCE REGISTER 2 (RMMR2)<br>ERROR REGISTER 2 (RMER2)<br>ECC POSITION REGISTER (RMEC1)<br>ECC PATTERN REGISTER (RMEC2)<br>BUS ADDRESS EXTENSION (RMBAE) | $\begin{array}{r} 4-3 \\ 4-3 \\ 4-3 \\ 4-4 \\ 4-6 \\ 4-8 \\ 4-10 \\ 4-11 \\ 4-11 \\ 4-12 \\ 4-13 \\ 4-13 \\ 4-13 \\ 4-14 \\ 4-14 \\ 4-15 \\ 4-16 \\ 4-16 \\ 4-17 \end{array}$ |

| 4.22                                                                                                                                                                                | CONTROL/STATUS REGISTER 3 (RMCS3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-17                                                                                                                                                                          |

| Sec | ti | on | 5 |

|-----|----|----|---|

|     |    |    |   |

COMMANDS

| 5.1   | DATA TRANSFER COMMANDS                           | 5-1 |

|-------|--------------------------------------------------|-----|

| 5.1.1 | Write Check Data (51)                            | 5-1 |

| 5.1.2 | Write Check Header and Data (53)                 | 5-2 |

| 5.1.3 | Write Data (61)                                  | 5-2 |

| 5.1.4 | Write Header and Data (Format<br>Operation) (63) | 5-2 |

| 5.1.5 | Read Data (71)                                   | 5-2 |

| 5.1.6 | Read Header and Data (73)                        | 5-2 |

| 5.2   | POSITIONING COMMANDS                             | 5-3 |

| 5.2.1 | Seek Command (5)                                 | 5-3 |

| 5.2.2 | Recalibrate (7)                                  | 5-3 |

| 5.2.3 | Offset Command (15)                              | 5-3 |

| 5.2.4 |                                                  | 5-4 |

| 5.2.5 | Search Command (31)                              | 5-4 |

| 5.3   | HOUSEKEEPING COMMANDS                            | 5-4 |

| 5.3.1 | No Op (1)                                        | 5-4 |

| 5.3.2 | Drive Clear (11)                                 | 5-4 |

| 5.3.3 | Release Command (13)                             | 5-4 |

| 5.3.4 | Read-In Preset (21)                              | 5-4 |

| 5.3.5 | Pack Acknowledge                                 | 5-4 |

| 5.4   | OPTIONAL COMMANDS                                | 5-5 |

| 5.4.1 |                                                  | 5-5 |

|       |                                                  | 5-5 |

| 5.4.2 | DMA Bandwidth Set (25)                           | 5-5 |

Section 6 BOOTSTRAP PROM OPTION

|          | 6.1   | OVERVIEW                                            | 6-1        |

|----------|-------|-----------------------------------------------------|------------|

|          | 6.2   | ODT BOOTSTRAP                                       | 6-2        |

|          | 6.2.1 | Operation                                           | 6-3        |

|          | 6.3   | Operation<br>AUTO BOOTSTRAP<br>Operation            | 6-4        |

|          | 6.3.1 | Operation                                           | 6-5        |

|          | 6.3.2 | Alternate Bootstrap Devices                         | 6-5        |

|          | 6.4   | PROGRAM MESSAGES                                    | 6-7        |

| Appendix | A     | SC03/Bl Configuration and Option Select:            | ion        |

|          | A.l   | INTRODUCTION                                        | A-1        |

|          | A.2   |                                                     | A-1        |

|          | A.2.1 |                                                     | A-1        |

|          | A.2.2 | Drive Configuration Selection                       | A-1        |

|          | A.3   | USER SELECTABLE OPTIONS                             | A-4        |

| Appendix | В     | Modification for DEC Diagnostics                    |            |

|          | B.1   | ZRMA-CO FORMATTER                                   | B-1        |

|          | B.1.1 |                                                     | B-1        |

|          |       | Errors                                              |            |

|          | в.1.2 | Modifications For Number of Cylinders               | B-1        |

|          |       | and Tracks                                          |            |

|          | B.1.3 | Formatter Operation                                 | B-2        |

|          | B.2   |                                                     | B-3        |

|          | B.2.1 | Modifications to Correct Programming                |            |

|          | B.2.2 | Errors<br>Modifications For Number of Culinders     | <b>D /</b> |

|          | D•2•2 | Modifications For Number of Cylinders<br>and Tracks | D-4        |

|          | B.2.3 |                                                     | B-5        |

|          | B.3   | ZRMC-B0 FUNCTIONAL TEST - PART 1                    | B-6        |

|          | B.3.1 | Modifications For Correct Operation                 |            |

|          | B.3.2 | Modifications For Number of Cylinders               |            |

|          | 21011 | and Tracks                                          | 20         |

|          | B.4   | ZRMD-B0 FUNCTIONAL TEST - PART 2                    | B-7        |

|          | B.4.1 | Modifications For Correct Operation                 | Б-7        |

|          | B.4.2 | Modifications For Number of Cylinders               |            |

|          | 2.1.2 | and Tracks                                          | D_0        |

|          | B.5   | ZRME-BO FUNCTIONAL TEST - PART 3                    | B <b>9</b> |

|          | B.5.1 | Modifications For Correct Operation                 | B-9        |

|          | B.5.2 | Modifications For Number of Cylinders               |            |

|          | D•J•Z | and Tracks                                          | B-9        |

|          | B.6   | ZRMF-BO EXTENDED DRIVE TEST                         | B-10       |

|          | B.6.1 | Modifications For Correct Operation                 | B-10       |

|          | B.6.2 | Modifications For Number of Cylinders               |            |

|          |       | and Tracks                                          | O T - C    |

|          | B.7   | ZRMI-BO DRIVE COMPATIBILITY TEST                    | B-11       |

|          | B.7.1 | Modifications For Correct Operation                 | B-11       |

|          | B.8   | EMULEX DIAGNOSTICS                                  | B-11       |

|          |       |                                                     |            |

# LIST OF TABLES

| <u>Table</u> | No.          | Title                                           | <u>Page</u> |

|--------------|--------------|-------------------------------------------------|-------------|

| Table        | 1-1          | General Specifications                          | 1-4         |

| Table        | 2-1          | Disk Drive Connections                          | 2-6         |

| Table        | 2-2          | Q-Bus Connections                               | 2-8         |

| Table        | 2-3          | Register Access on Dual Controller<br>Operation | 2-18        |

| Table        | 6-1          | Bootstrap Option Kit PROMs                      | 6-1         |

| Table        | 6-2          | ODT Boot Devices                                | 6-2         |

| Table        | 6-3          | Auto Bootstrap Device Priority List             | 6-4         |

| Table        | 6-4          | Alternate Boot Device Address                   | 6-6         |

| Table        | 6-5          | Boot Option Messages                            | 6-7         |

| Table        | A-1          | Drives Supported                                | A-2         |

| Table        | A-2          | Drive Configurations                            | A-3         |

| Table        | A-3          | SC03 Factory Switch Settings                    | A-4         |

| Table        | A-4          | Option Switch SWl Settings                      | A-5         |

| Table        | A-5          | Option Switch SW2 Settings                      | A-5         |

| Table        | A-6          | Option Switch SW3 Settings                      | A-6         |

|              |              | LIST OF FIGURES                                 |             |

| Figure       | <u>e No.</u> | Title                                           | Page        |

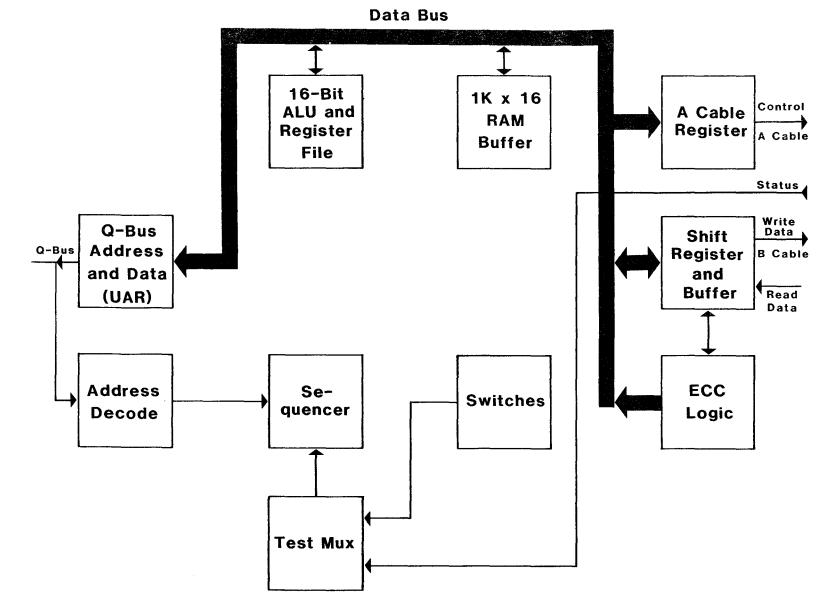

| Figure 2-1 | SC03 Block Diagram       | 2-2  |

|------------|--------------------------|------|

| Figure 2-2 | SC03 Controller Board    | 2-3  |

| Figure 2-3 | Sector Format            | 2-10 |

| Figure 2-4 | Header Format            | 2-10 |

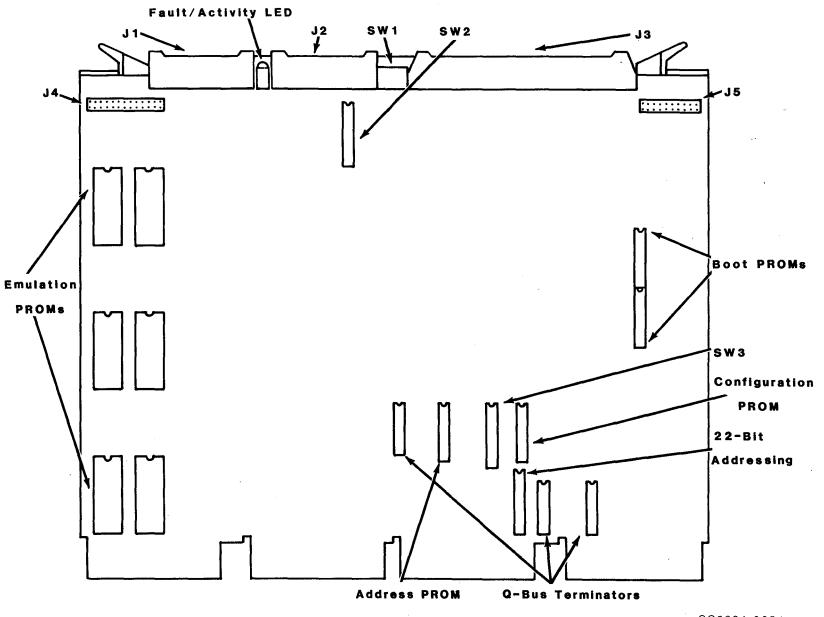

| Figure 3-1 | SC03 Controller Assembly | 3-3  |

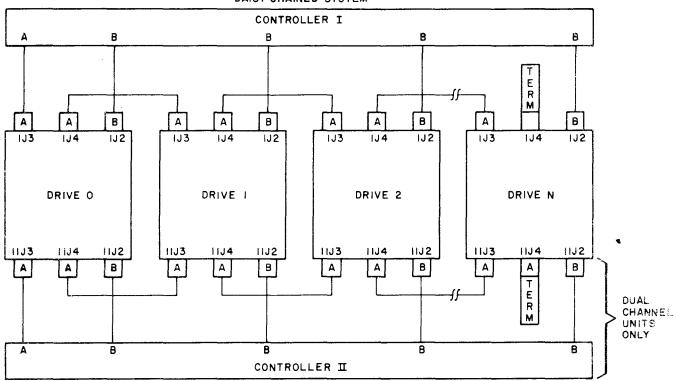

| Figure 3-2 | Cabling Schematic        | 3-7  |

BLANK

Section 1 INTRODUCTION

## 1.1 SCOPE

This manual provides information related to the capabilities, design, installation, and use of the SC03/Bl Disk Controller. In addition, this manual provides diagnostic and application information.

#### 1.1.1 Register Addresses in this Manual

The register addresses given in this manual are standard Q-Bus addresses for an RM disk subsystem. All addresses are given for an 18-bit Q-Bus. For 22-bit addressing add 17000000 to obtain the desired register address.

#### 1.2 OVERVIEW

## 1.2.1 General Description

The SC03/Bl Disk Controller is a one board, imbedded controller for LSI-11 computers manufactured by Digital Equipment Corporation. This controller can be used to interface any large disk having a Storage Module Drive (SMD) interface. The SC03/Bl controller emulates the RH11 and RH70 disk controllers manufactured by Digital Equipment Corporation for use with RM02, RM03, RM05, and RM80 disk drives.

## 1.3 FEATURES

## 1.3.1 Microprocessor Design

The SC03/Bl design incorporates a unique 16-bit bipolar microprocessor to perform all controller functions. The microprocessor approach provides for a reduced component count, high reliability, easy maintainability, and most importantly, the ability to adapt a single set of hardware to a wide range of emulation capabilities through the use of microprogramming. The Emulex controllers achieve functional capability beyond that of the DEC controllers which they emulate, by providing enhancement features such as built-in self-test during power-up, built-in disk formatting and the ability to work with disk drives of various sizes.

# 1.3.2 Packaging

The SC03/Bl is constructed on a single, quad-size, Multi-layer PC board which plugs directly into the LSI-ll chassis. No cabling is

required between the computer and the disk controller. The controller obtains its power from the chassis in which it is mounted.

### 1.3.3 Self-Test

The controller incorporates an internal self-test routine which is executed upon power-up. This test exercises all parts of the microprocessor, buffer and disk data logic. Although this test does not completely test all controller circuitry, successful execution indicates a very high probability that the controller is operational. If the controller fails the self-test, it leaves the LED ON and the controller cannot be addressed from the CPU.

#### 1.3.4 Buffering

The controller contains a 4K x 16 high-speed RAM buffer. It is used to store the device registers of the controller plus a 14 sector data buffer. The large buffer eliminates the possibility of a data late condition and permits the controller to be operated at low bus priorities.

## 1.3.5 Error Correction

The controller incorporates a 32-bit error correcting code (ECC) capable of correcting a single error bit in bursts of up to 11 bits in length and detecting multiple error bits in bursts of any length. The controller determines the pattern and location of the error so that the software may correct the data after it is transferred to memory. A 16-bit CRC is employed with the header of every sector.

## 1.3.6 Dual Port Mode

In order to provide compatibility with dual port drivers when configured for dual port, the dual port mode is provided. This mode should be selected only when the disk drive has dual ports and is configured for dual port operation.

#### 1.3.7 Dual Access Mode

In order to provide compatibility with dual access drivers when configured for dual access, the dual access mode is provided. When in this mode, the controller sets Dual Port Mode (Drive Type Register) and Programmable (Drive Status Register) to imitate the DEC neutral state.

Setting the Dual Port Option switch overrides the Dual Access Option except except for the one-second power-up timer disable.

#### 1.3.8 Option and Configuration Switches

Sockets provide for insertion of optional 512 word bootstrap PROMS, 22-bit addressing and Q-Bus termination resistor packs. Provisions

are also made to enable an optional software-controlled line time clock (LTC) which is BDV11 compatible.

DIP switches are used to configure the controller for various disk sizes, Q-Bus addresses and options. It is possible to select one of several possible combinations of disk characteristics for the two drives which can be handled by the controller, including mixtures of disk sizes and drive type codes.

#### 1.4 FUNCTIONAL COMPATIBILITY

# 1.4.1 Media Compatibility

In all cases, the headers written on the drives are standard RM02, RM03, RM05 and RM80 headers. Packs may be formatted by utilizing the hardware formatting capability of the extended command set. Disk packs formatted with an SC03/Bl controller are media compatible with other Emulex controllers and with the equivalent DEC packs when appropriate disk drives are used.

## 1.4.2 Disk Mapping

Depending upon the type and size of the disk drive, one or two logical units may be mapped on it. Various mapping organizations are used; some of which do not leave direct 1:1 correlation between the logical and physical addresses.

## 1.4.3 Diagnostics

The SC03/Bl will run the following DEC diagnostics on LSI-11 computers.

| ZRMA | Formatter |

|------|-----------|

|------|-----------|

- ZRMB Performance Exerciser

- ZRMC Functional Controller, Part I\*

- ZRMD Functional Controller, Part II\*

- ZRME Functional Controller, Part III\*

- ZRMF Extended Drive Test

- ZRMI Drive Compatibility Test

The diagnostics marked with an asterisk require certain patches to bypass unsupported maintenance functions. All diagnostics require patches to run with drive sizes other than that of a standard RM02/RM03. See Appendix B for diagnostic patches.

Emulex provides self-sizing diagnostics for the SC03. They are listed at the end of Appendix B.

## 1.4.4 Operating Systems

The SC03/Bl is compatible with all DEC operating systems running on LSI-ll computers that support the appropriate DEC disk subsystems. No operating system modifications are required when running standard sized disk drives.

# Table 1-1 General Specifications

-----

.

| FUNCTIONAL                               |                                                                                                               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Emulation                                | DEC RM02, RM03, RM05 and RM80                                                                                 |

| Media Compatibility                      | DEC RM02, RM03 and RM05 when using appropriate disk drives.                                                   |

| Drive Interface                          | SMD                                                                                                           |

| Drive Ports                              | 2                                                                                                             |

| Error Control                            | 32-bit ECC for data and 16-bit CRC for<br>headers. Correction of single data error<br>burst of up to 11 bits. |

| Sector Size                              | 256 words (512 bytes)                                                                                         |

| Sectors/Track                            | Selectable for each drive.                                                                                    |

| Tracks/Cylinder                          | Selectable for each drive.                                                                                    |

| Cylinders/Drive                          | Selectable for each drive.                                                                                    |

| Drive Type Code                          | Selectable for each drive.                                                                                    |

| Computer Interface                       | Q-Bus                                                                                                         |

| Q-Bus Address<br>Standard<br>Alternate   | 776700-776752<br>776300-776352                                                                                |

| Vector Address<br>Standard<br>Alternates | 254<br>50, 150, 270, 274, 354, 370, 374                                                                       |

| Priority Level                           | BR4                                                                                                           |

| Data Bufferring                          | 14 full sectors                                                                                               |

| Data Transfer                            | High speed NPR operation.                                                                                     |

| Maximum Disk Data Rate                   | 16 MHz (2 MBytes/second)                                                                                      |

| Self-TestExtensive internal self-test on powering<br>up.IndicatorsActivity/Fault LEDDESIGNHigh-speed bipolar microprocessor using<br>2901 bit slice components.PHYSICALPackagingPackagingOne DEC quad-size board.MountingAny slot in CPU or expansion box.ConnectorsOne 60-pin A cable flat connector and two<br>26-pin B cable connectors. (Flat cable<br>type.)ElectricalQ-Bus InterfaceDrive InterfacesDifferential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.Power+5 v, 8 Amp. max. |                  |                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------|

| DESIGN High-speed bipolar microprocessor using<br>2901 bit slice components.<br>PHYSICAL<br>Packaging One DEC quad-size board.<br>Mounting Any slot in CPU or expansion box.<br>Connectors One 60-pin A cable flat connector and two<br>26-pin B cable connectors. (Flat cable<br>type.)<br>Electrical<br>Q-Bus Interface DEC approved line drivers and receivers.<br>Drive Interfaces Differential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                          | Self-Test        |                                          |

| 2901 bit slice components.         PHYSICAL         Packaging       One DEC quad-size board.         Mounting       Any slot in CPU or expansion box.         Connectors       One 60-pin A cable flat connector and two 26-pin B cable connectors. (Flat cable type.)         Electrical       Q-Bus Interface         Drive Interfaces       Differential line drivers and receivers. A cable accumulative length to 35 feet. B cable length to 25 feet.                                                                                        | Indicators       | Activity/Fault LED                       |

| PackagingOne DEC quad-size board.MountingAny slot in CPU or expansion box.ConnectorsOne 60-pin A cable flat connector and two<br>26-pin B cable connectors. (Flat cable<br>type.)ElectricalQ-Bus InterfaceQ-Bus InterfaceDEC approved line drivers and receivers.<br>Drive InterfacesDifferential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                            | DESIGN           |                                          |

| MountingAny slot in CPU or expansion box.ConnectorsOne 60-pin A cable flat connector and two<br>26-pin B cable connectors. (Flat cable<br>type.)ElectricalQ-Bus InterfaceQ-Bus InterfaceDEC approved line drivers and receivers.<br>Drive InterfacesDifferential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                             | PHYSICAL         |                                          |

| ConnectorsOne 60-pin A cable flat connector and two<br>26-pin B cable connectors. (Flat cable<br>type.)ElectricalQ-Bus InterfaceDrive InterfacesDifferential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                                                                                                                                 | Packaging        | One DEC quad-size board.                 |

| 26-pin B cable connectors. (Flat cable<br>type.)<br>Electrical<br>Q-Bus Interface DEC approved line drivers and receivers.<br>Drive Interfaces Differential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                                                                                                                                  | Mounting         | Any slot in CPU or expansion box.        |

| Q-Bus Interface DEC approved line drivers and receivers.<br>Drive Interfaces Differential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                                                                                                                                                                                                    | Connectors       | 26-pin B cable connectors. (Flat cable   |

| Drive Interfaces<br>Differential line drivers and receivers.<br>A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                                                                                                                                                                                                                                                             | Electrical       |                                          |

| A cable accumulative length to 35 feet.<br>B cable length to 25 feet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q-Bus Interface  | DEC approved line drivers and receivers. |

| Power +5 v, 8 Amp. max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Drive Interfaces | A cable accumulative length to 35 feet.  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Power            | +5 v, 8 Amp. max.                        |

BLANK

## 2.1 CONTROLLER ORGANIZATION

A block diagram showing the major functional elements of the SC03/Bl controller is shown in Figure 2-1. The controller is organized around a 16-bit high-speed bipolar microprocessor. The ALU and register file portion of the microprocessor are implemented with four 2901 bit slice components. The microinstruction is 48 bits in length and the control memory of 2K words is implemented with six 2K x 8 PROMs.

The controller incorporates a 4K x 16 high-speed RAM buffer which is used to store the controller's device registers and 14 sectors of data buffering.

The A Cable Register (ACR) latches all A cable signals going to or from the disk drives. The inputs from the selected drive are testable by the microprocessor.

The Shift Register converts parallel write data from the data bus to serial data for the disk drives. The register also converts serial read data from the drives back into parallel data. Serial read and write data is provided to the ECC logic via the Shift Register.

Serial data from the drive is converted into eight-bit parallel data and transferred to the buffer via the microprocessor. Likewise, the data access from the buffer by the microprocessor is serialized and sent to the drive under the control of the servo clock received from the drive. A 32-bit ECC Shift Register is used to generate and check the ECC for the data field. The same register is also used in a 16-bit CRC mode for the headers. The actual ECC polynomial operation is done independently of the microprocessor, but the determination of the error position and error pattern is done under the control of the microprocessor.

The Q-Bus interface consists of 42 bidirectional lines (which include lines Al8 to A21) and two unidirectional signal lines. The Q-Bus interface is used for programmed I/O, CPU interrupts, and data transfers. The microprocessor responds to all programmed I/O and carries out the I/O functions required for the addressed controller register. The microprocessor also controls all DMA operations and transfers data between the Q-Bus data lines and the buffer.

## 2.2 PHYSICAL DESCRIPTION

The SC03/Bl controller consists of a single quad-size board which plugs directly into an LSI-11 chassis. The controller PCBA is shown in Figure 2-2.

SC0301-0079

Figure 2-1 SC03 Block Diagram

## 2.2.1 Connectors

## 2.2.1.1 A Cable Connector

The 60-pin flat cable connector labeled J3 at the top edge of the board is for the A cable which daisy-chains to all the drives for control and status. Pin 1 is located on the right side of the connector.

## 2.2.1.2 B Cable Connector

The two 26-pin flat cable connectors labeled Jl and J2 are for the radial B cables to each of two physical drives which may be attached to the controller. Pin l is identified by an arrowhead on the connector. The two B cable ports are identical and either drive may be plugged into either connector.

## 2.2.1.3 Test Connectors

Connectors J4 and J5 are used with the Emulex test panel during manufacturing test and factory repair. They have no use in normal operation.

# 2.2.2 Switches

There are three sets of switches labled SW1-SW3. SW1 is a four pole DIP "piano-type" switch accessible from the PC board edge. SW1 is located such that it is accessible to the operator while the controller is imbedded in an LSI type chassis, making the selection of common options simpler to perform.

The other two sets of switches SW2 and SW3 provide controller address decoding selection, option selection and drive configuration selection. (See Section 3 for a complete description of the switch functions.)

## 2.2.3 LED Indicator

There is an LED indicator mounted between the B Cable connectors at the top of the board. The controller executes an extensive self-test when powering up. The microprogrammed organization of the controller permits most logic other than the interface circuitry to the disk to be validated before the controller becomes ready. The LED lamp is turned ON as the controller starts its self-test and is turned OFF only when the controller successfully completes the test. If a malfunction is detected by the built-in diagnostics, the LED remains ON and the controller will not respond to program I/O. The LED blinks at approximately a one second rate if the self-test is successful but no drive is seen on-line. The LED also functions as an activity indicator during read and write operations.

## 2.2.4 Firmware PROMs

There are six PROM sockets, used for the control memory, located along the left edge of the board. The sockets are labeled PROM 0 through PROM 5 in a discontinuous physical order. The numbers on the top of the PROM ICs are Emulex part numbers, which identify the unique pattern of the PROM. When inserting PROMs in the board, the ID numbers are placed in the same sequence as the PROM numbers on the board beside each socket.

## 2.2.5 Bootstrap PROMs

There are two sockets provided for the installation of optional bootstrap PROMS. They are at location U71 and location U92. PROM number B02 or B04 goes in location U92, and PROM number B03 or B05 goes in location U71. The Emulex part number of the option kit is SC0313001. See paragraph 3.4.4.2 for installation instructions, and section 6 for operating instructions.

## 2.3 INTERFACES

## 2.3.1 Disk Interface

The controllers's disk interface conforms to the Flat Cable Interface Specification for the SMD, MMD, and CMD (CDC Document No. 64712400). The controller has been tested with most drives using the SMD, MMD and CMD interfaces and is compatible with these drives electrically and in timing.

The following defines the electrical interface and the recommended cables.

## 2.3.1.1 <u>A Cable</u>

The 60-conductor A cable is daisy-chained to all drives and terminated at the last drive. The signals in this cable are listed in Table 2-1 along with their function when the control tag (Tag 3) is asserted. The A cable should be a 30-twisted-pair flat cable with an impedance of 100 ohms and a cumulative length of no greater than 35 feet.

Spectra-Strip P/N 455-248-60 flat cable or its equivalent is recommended. It is possible to order A-Cable assemblies from Emulex that are made up in one of four lengths:

| EMULEX P/N                                              | LENGTH (FT.)                                                  |

|---------------------------------------------------------|---------------------------------------------------------------|

| SU1111201<br>SU1111203<br>SU1111205<br>SU1111207        | 8.0<br>15.0<br>25.0<br>35.0                                   |

| سے ہے جو سر سے سے طو میں سو سو سے جو سو سر میں دی جو سر | دی میں غیر ہیں منڈ کٹر خص نے میں میں غیر غنو من میں جلا میں ا |

2-5

# Table 2-1 Disk Drive Connections

| Pins Lo/Hi                | Signal             | (Tag 3 Function)     | From/To  |

|---------------------------|--------------------|----------------------|----------|

| A Cable:                  |                    |                      |          |

| 22,52                     | Unit Select Tag    |                      | То       |

| 23,53                     | Unit Select bit (  | )                    | То       |

| 24,54                     | Unit Select bit 1  | L                    | То       |

| 26,56                     | Unit Select bit 2  | 2                    | То       |

| 27,57                     | Unit Select bit 3  | 3                    | To       |

|                           | Tag l              |                      | То       |

| 2,32                      | Tag 2              |                      | То       |

| 3,33                      | Tag 3              |                      | То       |

| 4,34                      | Bit O              | (Write Gate)         | То       |

| 5,35                      | Bit l              | (Read Gate)          | То       |

|                           | Bit 2              | (Servo Offset Plus)  | To       |

|                           | Bit 3              | (Servo Offset Minus) | To       |

|                           | Bit 4              | (Fault Clear)        | To       |

|                           | Bit 5              | (AM Enable)          | То       |

| 10,40                     | Bit 6              | (Return to Zero)     | TO       |

| 11,41                     | Bit 7<br>Bit 8     | (Data Strobe Early)  | То       |

| 12,42                     |                    | (Data Strobe Late)   | То       |

|                           | Bit 9<br>Bit 10    | (Release)            | To<br>To |

|                           | Open Cable Detect  |                      | To       |

| 15,45                     |                    |                      | From     |

|                           | Seek Error         |                      | From     |

|                           | On Cylinder        |                      | From     |

| 18,48                     |                    |                      | From     |

| 19,49                     |                    |                      | From     |

| 20,50                     |                    |                      | From     |

| <sup>20,50</sup><br>21,51 | Busy (dual port of | ( <b>1 1 1</b>       | From     |

| -                         | Sector             | JIILY)               | From     |

|                           | Write Protected    |                      | From     |

| 29                        |                    | old.                 | To       |

| 59                        | Power Sequence Pi  |                      | To       |

|                           |                    |                      |          |

|                           |                    |                      |          |

| B Cable:                  |                    |                      |          |

| 8,20                      | Write Data         |                      | То       |

| 6,19                      | Write Clock        |                      | TO       |

| 2,14                      | Servo Clock        |                      | From     |

| 3,16                      | Read Data          |                      | From     |

| 5,17                      | Read Clock         |                      | From     |

| 10,23                     | Not Used           |                      | From     |

| 22,9                      | Unit Selected      |                      | From     |

| 12,24                     | Not Used           |                      | From     |

| 13,26                     | Not Used           |                      | From     |

|                           |                    |                      |          |

## 2.3.1.2 B Cable

The 26-conductor B cable is radial to all drives and contains the data and clock signals. The signals and grounds in this cable are listed in Table 2-1. The B cable should be 26 conductor flat cable with ground plane and drain wire. The impedance should be 130 ohms and the length must not be greater than 25 feet.

3M-P/N 3476/26 flat cable or its equivalent is recommended. It is possible to order B-cable assemblies from Emulex that are made up in one of three lengths:

| EMULEX P/N | LENGTH (FT.) |

|------------|--------------|

| SU111202   | 8.0          |

| SU111204   | 15.0         |

| SU111206   | 25.0         |

## 2.3.2 Q-Bus Interface

The LSI-ll Bus consists of 42 bidirectional and 2 unidirectional signal lines. These form the lines along which the processor, memory and I/O devices communicate with each other.

Addresses, data, and control information are sent along these signal lines, some of which contain time-multiplexed information. The lines are divided as follows:

- 1. Sixteen data/address lines <BDAL00:BDAL15>

- 2. Six address lines <BDAL21:BDAL16>

- Six data transfer control lines BBS7, BDIN, BDOUT, BRPLY, BSYNC, BWTBT

- Three direct memory access control lines BDMGI, BDMR, BSACK

- 5. Six interrupt control lines BEVENT, BIAKO, BIRQ4, BIRQ5, BIRQ6, BIRQ7

- Five system control lines BPCOK, BHALT, BINIT, BPOK, BREF.

The MS four data/address lines (BDAL <21:18>) are used only for addressing and do not carry data. BDAL <17:16> reflect the parity status of the 16-bit data word during the data transfer portion of the bus cycle.

# Table 2-2 Q-Bus Connections

|          | A      | L      | В      |        |

|----------|--------|--------|--------|--------|

|          | 1      | 2      | 1      | 2      |

| <u>а</u> | BIRQ5  | +5V    | BPCOK  | +5V    |

| В        | BIRQ6  |        | BPOK   |        |

| С        | BDAL16 | GND    | BDAL18 | GND    |

| D        | BDAL17 |        | BDAL19 |        |

| E        |        | BDOUT  | BDAL20 | BDAL02 |

| F        |        | BRPLY  | BDAL21 | BDAL03 |

| H        |        | BDIN   |        | BDAL04 |

| J        | GND    | BSYNC  | GND    | BDAL05 |

| K        |        | BWTBT  |        | BDAL06 |

| L        |        | BIRQ4  |        | BDAL07 |

| М        | GND    | BIAKI  | GND    | BDAL08 |

| N        | BDMR   | BIAKO  | BSACK  | BDAL09 |

| Ρ        | BHALT  | BBS7   | BIRQ7  | BDAL10 |

| R        | BREF   | BDMGI  | BEVENT | BDAL11 |

| S        |        | BDMGO  |        | BDAL12 |

| Т        | GND    | BINIT  | GND    | BDAL13 |

| U        |        | BDAL00 |        | BDAL14 |

| v        |        | BDAL01 |        | BDAL15 |

|          |        |        |        |        |

### 2.3.2.1 Interrupt Priority Level

The controller is hardwired to issue level 4 interrupt requests and monitor level 5. The level 4 request is necessary to allow compatibility with either a LSI-11 or LSI-11/2 processor.

#### 2.3.2.2 Register Address

The register address and the number of registers assigned to the controller are decoded by a PROM at U124. The selections available are determined by configuration switches SW3-7 and SW3-8 as discussed in Section 3.

## 2.3.2.3 DCOK and INIT Signals

The DCOK and INIT signals both perform a controller clear. The self-test is performed only when DC power is initially applied.

#### 2.4 DISK FORMAT

#### 2.4.1 Disk Pack Organization

The formatting of a disk pack and the mapping of one or two logical drives onto a physical drive varies with the drive size. Some of this information is supplied by the configuration PROM. The rest is computed based upon configuration PROM information.

## 2.4.2 Mapping

Depending upon the type and size of the disk drive, one or two logical units may be mapped on it. The controller can handle a maximum of four logical units distributed across a maximum of two physical drives. A logical drive may not be mapped across a physical unit boundary.

In most cases there is a 1:1 correspondence between logical and physical disk addresses. The controller has the capability to alter a logical address to a different physical address in order to accommodate drives that do not match the number of tracks and cylinders for the RM unit being emulated.

### 2.4.3 Sector Organization

Figure 2-3 shows the typical sector format used by the controller. Each track of 20,160 bytes is divided into 32 sectors of 630 bytes. The four byte header is preceded by a preamble of 30 bytes ending in the sync byte and is followed by a two byte CRC. The 256-word data field is preceded by a preamble of 20 bytes ending in the sync byte, and is followed by four bytes of ECC. This format is compatible with that of the DEC RM02, RM03, RM05, and RM80.

If the actual size of the useful data information is less than 256 words, the remainder of the data field will be filled with 0's until 256 words have been written. During disk formatting

procedures, each data track is located and recorded with header information by means of the Write Header and Data command. A disk pack should be formatted and the format verified before any real data is written on it. Once formatted, individual or groups of sectors should not be reformatted unless absolutely necessary.

----- Sector Length 630 Bytes -----

| Preamble Sync               | Header | CRC | Preamble | Sync | Data Field | ECC | Recovery |  |  |

|-----------------------------|--------|-----|----------|------|------------|-----|----------|--|--|

|                             |        |     |          |      |            |     |          |  |  |

| Figure 2-3<br>Sector Format |        |     |          |      |            |     |          |  |  |

Header Word 1:

| _15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07  | 06   | 05   | 04   | 03 | 02 | 01 | 00 |

|-----|----|----|----|----|----|----|----|-----|------|------|------|----|----|----|----|

| 1   | 1  | 0  | 1  | 0  |    |    |    | Cyl | inde | r Ad | dres | S  |    |    |    |

Header Word 2:

| 15            | 14 | 13 | 12  | 11  | 10   | 09 | 08 | 07 | 06 | 05 | 04   | 03   | 02   | 01   | 00_ |

|---------------|----|----|-----|-----|------|----|----|----|----|----|------|------|------|------|-----|

|               |    |    | m e | aak | 744~ |    |    |    |    |    | C    |      | ~ 74 | drog |     |

| Track Address |    |    |     |     |      |    |    |    |    | 5  | ecto | r Ad | ares | S    |     |

|               |    |    |     |     |      |    |    |    |    |    |      |      |      |      |     |

Header Word 3:

| 15 | 14 | _13 | 12 | 11 | 10   | 09  | 08   | 07  | 06   | 05  | 04 | 03 | 02 | 01 | 00 |

|----|----|-----|----|----|------|-----|------|-----|------|-----|----|----|----|----|----|

|    |    |     |    |    |      |     |      |     |      |     |    |    |    |    |    |

|    |    |     |    | Су | clic | Ređ | unda | ncy | Code | (CR | C) |    |    |    |    |

|    |    |     |    |    |      |     |      |     |      |     |    |    |    |    |    |

Figure 2-4 Header Format

## 2.4.4 Header

## 2.4.4.1 Header Description

Figure 2-4 shows the header format, which consists of the following three words:

- Word One: This word contains the cylinder address. It contains a 1 in bit 12 to identify 16-bit format to the software and 1-bits in bit positions 14 and 15 to identify a good sector. For RM80 emulations only, bit 13 will contain a 1-bit to identify skipped sectors and a 0-bit for normal sectors.

- Word Two: The low-order eight bits of this word contain the sector address. Each track on the drive typically contains 32 sectors. The upper byte of this word contain the track address.

- Word Three: This is the CRC word which is generated and checked by the controller logic. This word is not available to the software.

#### 2.4.4.2 Header Field Handling

After the drive reports that it is on cylinder, the controller locates the desired sector by means of the sector counters. The sector counters for each drive are maintained in the controller. The controller compares the first two words of the header against the desired track, sector and cylinder and then checks the CRC word for errors. An error in the header field is indicated by turning on the appropriate error bit in the error register (format error, header compare error, bad sector error, skip sector error or CRC A header error is only valid when the sector count field error). of the RMLA register and the sector field of the RMDA have already matched. It is immaterial where a CRC error occurs in the header field since the controller cannot determine its location in the field. However, software may read the header to memory by means of a Read Header and Data command. The header compare may be inhibited by setting the HCI bit in the RMOF register.

#### 2.5 GENERAL PROGRAMMING INFORMATION

### 2.5.1 Clearing the Controller

The controller has the following clearing methods:

a. <u>Controller Clear</u> - Controller Clear is performed by writing a 1-bit into the CLR bit (bit 05 of RMCS2) or Q-Bus INIT. This causes the following to be cleared:

- o RMCS1 bits <15:12>, <10:08>, <06:00>; RMCS2 bits

<15:07>, <05:00>; RMBA bits <15:00>; RMBAE bits

<05:00>; RMCS3 bits <15:04>. Sets RMCS2 bit 06 and

RMCS1 bit 07.

- o In all drives: RMER1; RMER2; RMDA; RMAS ATA bit; RMEC2; RMDS ATA, ERR and LST bits; RMMR1 bits <15:04>, <02:00>. Sets bit 03 of RMMR1.

- b. Error Clear The Error Clear is performed by writing a l-bit into the TRE bit (bit 14 of RMCS1). This causes a clearing of RMCS1 bits 13 and 14, bits <15:08> of RMCS2 and bits <15:11> of RMCS3. Clears the SC bit (bit 15 of RMCS1) if RMAS=0.

- c. <u>Drive Clear</u> The Drive Clear is a command (Code 11). This causes the following registers in the drive selected by U2-U0 to be cleared:

- RMER1; RMER2; RMAS ATA bit; RMEC2; RMDS ATA and ERR bits; RMMR1 bits <15:04>, <02:00>. Sets bit 03 of RMMR1.

## 2.5.2 Interrupt Conditions

The controller generates an interrupt on the following conditions:

- a. Upon termination of data transfer if interrupt enable is set when the controller becomes ready.

- b. Upon assertion of attention or occurence of a controller error (SC being set) while the controller is not busy and the interrupt enable is set.

- c. When the program writes 1 into IE and RDY at the same time. Note that this can be done by Read-Modify-Write instructions (BIS, BIC, etc.) which set the IE bit.

## 2.5.3 Termination of Data Transfers

A data transfer which has been successfully started may terminate in the following ways:

- a. <u>Normal Termination</u> Word count overflows to 0 and the controller becomes ready at the end of the current sector.

- b. <u>Controller Error</u> An error occurs in the RMCS2 register bits <15:08>. Any of these errors sets TRE which terminates the data transfer immediately and makes the controller ready.

- c. <u>Drive Error</u> The ERR bit in the RMDS register and at least one bit in an RMER1 or RMER2 register are set. TRE is also set and the controller becomes ready. The ATA for the drive doing the data transfer becomes asserted.

- d. <u>Program-Caused Abort</u> By performing a Controller Clear or a RESET instruction, the program can cause an abort of any operation. Status and error information is lost when this is done, and the controller and drive become ready immediately.

## 2.5.4 Ready Bits

RDY is the ready indicator for the controller. When RDY = 1, the controller is ready to accept a data transfer command. RDY is reset when the controller is doing a data transfer command. DRY is the ready indicator for the selected drive and is the complement of the drive's GO bit. To successfully initiate a data transfer command, both of these bits must be asserted. However, a non-data transfer command (Search, Drive Clear) may be issued to a drive at any time DRY is asserted regardless of the state of the RDY bit.

When a data transfer command is successfully initiated, both RDY and DRY become negated. When a non-data transfer command is successfully initiated, only DRY bit becomes negated.

The assertion of RDY after the execution of a data transfer command will not occur until the DRY bit is set and the controller is done. RDY is asserted on the completion of the last memory cycle (or at the time of an abort condition) and the last disk transfer.

If any command other than Drive Clear is issued to a drive which has ERR asserted, the command is ignored by the drive. If a Data Transfer command is issued to a drive which has ERR asserted, the drive does not execute the command and the missed transfer error (MXF, bit 09 in RMCS2 register) is set.

## 2.5.5 22-Bit Memory Addressing

Twenty-two-bit addressing capability is available as an option for the SC03/Bl. The Emulex part number for the option kit is SC0313002. The kit consists of a single AMD2908 IC which is placed in socket U150 on the SC03 PCBA.

The controller can be switched from an RH11 mode (18-bit addressing) to an RH70 mode (22-bit addressing) by closing SW2-3. This will allow access to the RMBAE and RMCS3 registers which are a part of the RH70 only.

#### WARNING

Some manufacturers of Q-Bus backplanes use the backplane lines now devoted to extended addressing for power distribution. Installing an SCO3 with the extended addressing option in such a system will damage the option IC. Before installing the option confirm that there is neither positive nor negative potential between lines BC1, BD1, BE1, BF1 and logic ground. An SCO3 without the addressing option will not be damaged if power is present on those lines.

#### 2.5.6 Line Time Clock (LTC)

The Line Time Clock is a 60 Hz clock generated by the power supply and distributed on the backplane as the BEVNT signal. A high to low transition of this signal interrupts the processor. BEVNT has the highest external interrupt priority; only processor interrupts have higher priorities. If external interrupts are enabled (PS bit 07 = 0), the processor PC (R7) and PS words are pushed onto the processor stack. The LTC (or external event device) service routine is entered by vector address 100; the usual interrupt vector adddress input operation by the processor is not required since vector 100 is generated by the processor.

The LTC can be software controlled by using the Line Clock Register on the SC03/BL. The Line Clock Register has a bus address of 777546. It is a one-bit, write-only register. Reads to this register return all-zero data. Bit 06 is the only bit implemented. A write to this register with bit 06 set enables the line clock. A write to this register with bit 06 reset disables the line clock. The enable bit need not be set again after an interrupt has been processed. The clock will continue to interrupt until bit 06 is reset or an INIT is generated.

See paragraph 3.4.4.4 for information on how to configure the processor for use with the LTC.

#### 2.5.7 Bootstrap Routines

Installing the Emulex bootstrap option kit (number SC0313001) makes available two bootstrap routines: the standard console bootstrap and auto-boot sequence. See paragraph 3.4.4.2 for installation instructions, and section 6 for operating instructions.

## 2.6 DUAL CONTROLLER OPERATION

SMD drives may be equipped with a dual port option which provides the capability for two controllers (generally on separate computers) to access the drive. The SC03/Bl controller supports this type of operation as a standard feature. This mode of controller operation is selected by setting SW2-6 ON. Most of the dual port functions of the DEC controller being emulated are supported, and those which are not should be transparent to a properly written dual port driver. Table 2-4 summarizes the controller register responses in dual port operation.

## 2.6.1 <u>Dual Port Drives</u>

The two drive ports are known as Channel I and Channel II. Because only one controller may access the drive at a time, access is granted on a first-come, first-served basis. Once a controller has gained access to the drive, the other controller is denied access until the first controller's operation is complete. However, each channel has a physical disable switch which can disable the port and prevent the associated controller from having access to it.

## 2.6.2 Unseized State

The drive is in the unseized state when it is not connected to either controller. The CPU must issue a request for the controller to seize the drive. This request is done in one of the following ways:

- a. Writing into any drive register, including read-only registers.

- b. Writing a one-bit into the drive's ATA bit in RMAS. The bit does not have to be set.

## 2.6.3 <u>Seized State</u>

The drive is seized when it is logically connected to one of the controllers. At that time DVA (RMCS1, bit 11) is set indicating that the drive is ready to communicate with the controller which has seized it. If the drive has already been seized by the other controller, then the DVA bit will not set, all the drive registers will read as zeros and any write to a register will be ignored. Attempts to seize a drive which is busy with the other port are remembered and then acted upon when the drive is released by the other controller.

#### 2.6.4 <u>Returning to the Unseized State</u>

The drive is released and returned to the unseized state by issuing a release command. In addition, a one second timer in the controller will timeout and release the drive if one of the events listed in section 2.6.2 for seizing the drive is not performed periodically to keep resetting the timeout timer. Reading the RMCS1 register will also reset the timeout timer if the drive is currently seized. This allows the CPU to check a drive's seized state, and if seized, not have to worry about a time-out release occurring.

When the controller sees a previously busy drive becoming unseized, it checks its request flag. If the flag is set (the drive had been requested while busy on the other port), the controller will seize the drive and set ATA causing an interrupt to the CPU if the IE bit is set. If the CPU does not respond to the attention within one second the drive will be released, but ATA remains set.

## 2.6.5 DEC Compatibility

The SC03/Bl controller differs from the equivalent DEC controller in three important areas.

First, there is no neutral state. Since the SC03 does not have instantaneous access to all drives at the same time (a limitation of the daisy-chained A cable and the microprocessor organization of the controller), the controller assumes the drive is busy on the other port if the controller has not already seized it. Thus, a read of RMCS1 will always indicate that the drive is seized by the other controller (DVA, bit 11 equals zero) unless the drive has been previously requested. The CPU must request the drive by writing into any drive register and wait until the ATA bit is set which indicates that the controller has seized the drive. If the drive was in reality not seized by the other controller, this will happen almost immediately. The DEC controllers, however, can switch from neutral to seized state within the time required to do a single read or write of a drive register. Thus, if the drive is not already seized, no ATA is set and the drive is immediately available to the seizing controller.

Second, the release command is not instantaneous since the controller takes a few microseconds to execute the command. During this time the drive will appear to be unseized.

Third, during a data transfer the timeout timers will not operate and the drives can not be polled to see if they are not busy. Therefore no drives are seized or released during the execution of a data transfer.

The software driver should not issue a Release command and then attempt to save the current status of a drive, since the Release command will immediately show the drive in the unseized state, thus returning zero data for the drive registers. In order to allow the other controller time to poll the drive, the CPU should not communicate with any of the released drive's registers until required to seize the drive again.

# 2.6.6 <u>Dual Port Drives in Single Port Mode</u>

When using an operating system which does not have dual port drive software support, it may still be advantageous to use dual port drives while operating in the controller in single port mode. This will allow for a non-dynamic type of operation between two CPUs. In this type of operation the controller does not unseize the drive and, in effect, it is seized by both controllers all the time. The one second timeout timer (and the release command) operate exactly as stated in Paragraph 2.6.4. Even when released, a drive will still appear to be seized to the releasing controller. No attention is generated when the other controller finds the drive not busy. Should a command be issued to a controller while a drive is busy on the other port, the controller will wait until the drive becomes unbusy before executing the command. No timer exists in this case.

This mode of operation eliminates the need for manually switching the drive from one controller to another.

#### 2.6.7 Dual Access Mode

In order to provide compatibility with dual access software, the dual access mode is provided (SW2-7 ON). When in this mode, the controller sets Dual Port Mode (Drive Type Register) and Programmable (Drive Status Register) to imitate the DEC neutral state.

When DPM and PGM are set, the operating system will attempt to seize a drive by simply writing a command to it. If the drive is unbusy the command is executed. If the drive is already busy on its other port, the controller simply waits until it is released and then seizes and commands it. Software timers are sufficiently long to prevent causing a timeout when it is forced to wait.

The first time the SCO3 sees a drive, it is ignored for one second. This one-second stall occurs once for each drive on the controller. It prevents the controller from seeing erroneous status information when power is applied to the drive after the controller has been powered-up. For a drive in dual port mode the stall will prevent the other CPU from accessing the drive until the stall completes. The dual access option switch bypasses the stall in all cases. For proper system operation with the dual access option switch ON, all drives must have power applied before either controller is powered-up.

Setting the Dual Port Option switch overrides the Dual Access Option.

#### 2.6.8 Dual Port Drives Busy Signal

When operating dual port drives it is necessary to unbias the busy signal. This is accomplished by setting SW2-9 OFF (open). When operating single port drives it is necessary to bias-off the undriven busy signal. This is accomplished by setting SW2-9 ON (closed). In two-drive configurations both drives must be of the same type (i.e., either both dual port or both single port dives). A dual port drive cannot be properly run with a single port drive that does not drive the busy signal on the A cable.

#### Table 2-3

### Register Access on Dual Controller Operation

<u>Controller Action</u> Response With Respect To Action On Ch. I Drive State:

#### Read RMCS1

Drive Not Seized: Reads the controller portion of the RMCS1 only. The drive's portion is read as all zeros. No request flag is set.

Drive Seized by Ch. I: DVA = 1; reads the register. Resets timer.

Drive Seized by Ch. II: Reads the controller portion of RMCS1 only. The drive's portion is read as all zeros. No request flag is set.

## Read any other drive register

Drive Not Seized: Reads all zeros.

Drive Seized by Ch. I: Reads the register.